令和6年度全国発明表彰 受賞発明・意匠概要(敬称略)

(第一表彰区分一覧へ/第二表彰区分一覧へ)

経済産業大臣賞

半導体パッケージの高密度化を実現する絶縁膜用組成物の発明(特許第5841373号)

| 藤田 充 | 旭化成株式会社 ライフイノベーション事業本部 電子マテリアル事業部 電子材料技術開発部 副部長 | |

| 平田 竜也 | 旭化成株式会社 元 ライフイノベーション事業本部 電子マテリアル事業部 電子材料技術開発部 | |

| 森田 涼子 | 元 旭化成株式会社 ライフイノベーション事業本部 電子マテリアル事業部 電子材料技術開発部 |

発明実施功績賞

| 工藤 幸四郎 | 旭化成株式会社 代表取締役社長 |

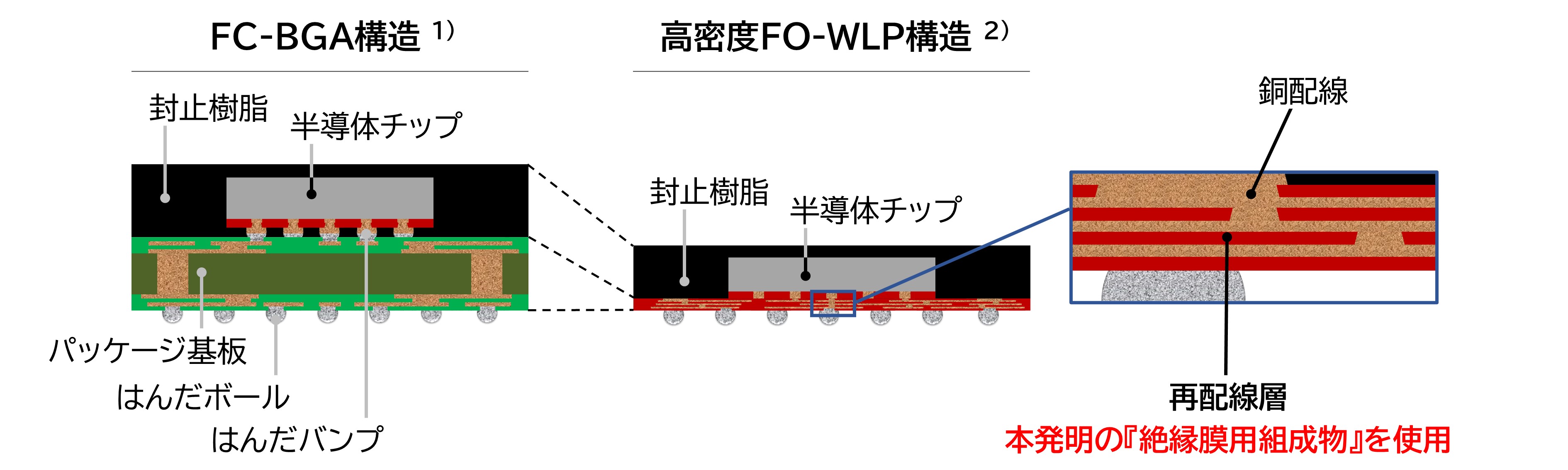

本発明は、高密度Fan-Out Wafer Level Package(高密度FO-WLP)の再配線層に用いられる絶縁膜用組成物に関するものである(図1)。

高密度FO-WLP構造では、封止樹脂の耐熱性の観点から、再配線用の絶縁樹脂は低温硬化が必要となり、銅配線との密着性が低下する。さらに再配線層にかかる応力が大きいことから、銅配線と絶縁樹脂間の剥離の問題もあり、既存の絶縁樹脂では実用化に至っていなかった。

への高い密着性を示し、かつ、防錆性を高いレベルで両立できる絶縁膜用組成物を見出した。加えて、

プリン誘導体が、従来使用されていた含窒素芳香族化合物とは異なるメカニズムで密着性と防錆性の

向上に寄与していることも解明した。

本発明の絶縁膜用組成物は、世界の最先端スマートフォンに使用され、一段とその適用範囲が広がり、電子デバイスの進化を日本の材料技術が牽引している代表的な例となっている。

|

| 図1 | 高密度FO-WLP構造への転換 *1) Flip Chip-Ball Grid Array Package(FC-BGA), *2) 高密度Fan-Out Wafer Level Package(高密度FO-WLP) |

|

| 図2 本発明の実施製品 |