文部科学大臣賞

低コスト高信頼性配線形成方法(特許第4771783号)

[宮崎県発明協会]

是沢 博史 |

ラピスセミコンダクタ宮崎株式会社 生産本部 AP製造部 再配線技術グループ グループリーダー |

岩元 延隆 |

ラピスセミコンダクタ宮崎株式会社 品質保証部 品質保証グループ サブグループリーダー |

実 施 功 績 賞

岡田 憲明 |

ラピスセミコンダクタ株式会社 代表取締役社長 |

鶴田 敬 |

ラピスセミコンダクタ宮崎株式会社 代表取締役社長 |

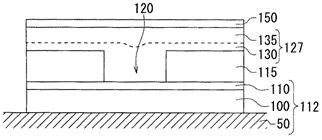

本発明は、高性能なアナログ回路、デジタル回路、ハイパワーMOSFETを一つの半導体チップ内に混載することで高機能ICを実現するBCDプロセスのCMOS領域に要求される微細なコンタクトホールの埋め込みとバイポーラ/DMOS領域の縮小においても高い電流密度を確保するための厚膜配線とを実現し、さらには車載用半導体に要求される高い信頼性を確保するものである。

本発明によれば、微細なコンタクトホールに使用される高融点金属を材料とするプラグを使用することなく、微細なコンタクトホールの埋め込み性を維持しつつ、膜厚の厚いメタルに生じるホイスカの発生を抑制するという課題の両立が可能となる。

これらの効果により、製造工程のコスト上昇を抑えつつサイズが縮小された半導体装置を製造することが可能となり、また半導体装置の信頼性低下を抑制することが可能となる。

Copyright©1996- Japan Institute of Invention and Innovation All rights reserved