関東経済産業局長賞

部分再構成を可能とする再構成可能デバイス(特許第4844406号)

【神奈川県発明協会】

山田 和雄 |

富士ゼロックス株式会社 研究技術開発本部 基盤技術研究所 |

実 施 功 績 賞

栗原 博 |

富士ゼロックス株式会社 代表取締役社長 |

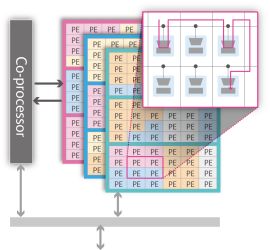

本発明は、高速処理を行う様々な種類の演算器(PE:Processor Element)を内蔵した動的再構成プロセッサ(DRP:Dynamically Reconfigurable Processor)に関する技術である(図1)。

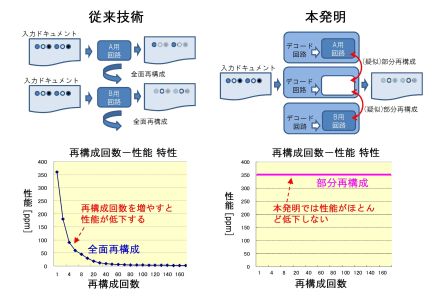

従来の全面再構成方式では、画像処理の種類毎にPEで構成された回路の再構成と入力ドキュメントの読み出しとが必要であった。そのため、画像処理を行う種類の分だけ入力ドキュメントの読み出し回数が増加し、総処理時間が長くなっていた。

本発明により、全面再構成方式であっても疑似的に部分的な再構成だけで済むので、入力ドキュメントの読み出しを再度行うことなく、継続して画像処理を実施することが可能となった。これにより、DRPの性能を飛躍的に向上させ、総処理時間を大幅に短縮することができた(図2)。

本発明を搭載した製品では、従来製品に比べ約2倍の画像処理性能を実現した。さらに、本発明は、DRPのみならずFPGAに代表される再構成デバイスへも適用可能であり、再構成が頻繁に生じるDeep Learning技術へ応用が期待されるため、自動車、ロボット、金融、IoT等の市場でも必須となり、その潜在的なポテンシャルは計り知れない。

Copyright©1996- Japan Institute of Invention and Innovation All rights reserved