日本弁理士会会長奨励賞

CMOSセンサのシェーディング低減技術(特許第3467013号)

【発明協会(東京)】

小泉 徹 |

キヤノン株式会社 デバイス開発本部 半導体デバイス製品開発センター 室長 |

光地 哲伸 |

キヤノン株式会社 デバイス開発本部 半導体デバイス製品開発センター 室長 |

米田 智也 |

元キヤノン株式会社 |

須川 成利 |

元キヤノン株式会社 |

実 施 功 績 賞

御手洗 冨士夫 |

キヤノン株式会社 代表取締役会長兼社長 CEO |

本発明は、デジタルカメラのキーコンポーネントであるCMOSセンサの画素領域における基準電圧供給のための構造を工夫することで、撮像画面内に発生するシェーディングを抑制し、撮影画像の画質向上を実現した発明である。

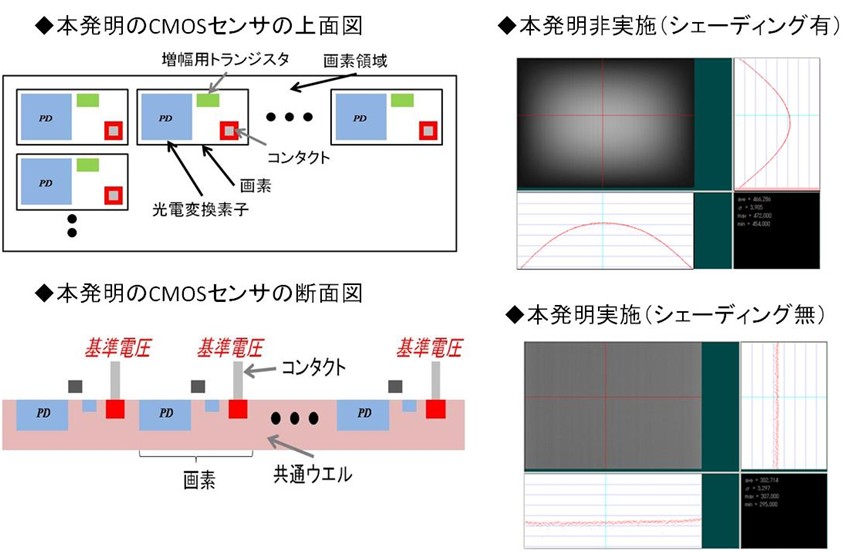

CMOSセンサでは光電変換素子と増幅用トランジスタとを有する画素が複数配されて画素領域を形成している。光電変換素子と増幅用トランジスタは共通ウエルに配される。

本発明は、この画素領域に設けられた共通ウエルに、複数の箇所から基準電圧を供給することで、共通ウエルに生じるセンサ内の位置に応じた電位分布の変化を抑制し、この電位分布の変化によって生じるシェーディングを抑制したものである。

本発明非実施のCMOSセンサでは撮像画面の中心部分にピークを有するシェーディングが発生していたが、本発明実施のCMOSセンサではこの様な画像のシェーディングが低減され、撮影画像の画質向上と、撮像画面の大面積化を両立することができた。

Copyright©1996- Japan Institute of Invention and Innovation All rights reserved